### Future Missions to Titan: Scientific and Engineering Challenges Low-Temperature Electronics: Opportunities for Titan Science

### John D. Cressler

Ken Byers Professor School of Electrical and Computer Engineering Georgia Tech, Atlanta, GA 30332-0250 USA cressler@ece.gatech.edu

KISS, Titan Study, Cal Tech, May 2010

This work was supported by NASA, DTRA, IBM, DARPA, JPL, TI, and NSC.

John D. Cressler, 5/10

### Remember ...

# There is No Such Thing as Doing Interesting Science on Titan (Physics, Chemistry, Geology Biology, etc.) ...

# Without a Robust Electronics Infrastructure!

# A Personal Mandate: We Need to Get Rid of That Darn Warm Box!

# HOW?!

#### • **Pro's** for Cooling Electronic Devices and Circuits:

- mobility increases (depends on doping)

- current drive increases

- saturation velocity increases

- latchup in CMOS improves (BJT gain drops)

- thermally-activated failure mechanisms improve (e.g., electromigration)

- subthreshold swing and transconductance improve

### • **Con's** for Cooling Electronic Devices and Circuits:

- carrier freeze-out can become an issue (depends on doping)

- breakdown voltages degrade

- hot carrier effects much stronger and can lead to major reliability issues

- heavy ion induced latchup in CMOS looks like a possibility (2010)

- TCAD simulation and compact modeling is a real challenge

- testing is painful

- cycling presents issues for electronic packaging

## **Technology Options**

Assumptions:

- foundry supported (commercially available via MPW)

- low cost

- must support high levels of integration (e.g., mixed-signal SoC)

- can enable robust operation of complex electronics at 93K

### **Technology Options / Comments:**

### Bulk Si CMOS

- most performance metrics improve with cooling

- cryo-T hot carrier lifetime is a serious issue to address

- best for digital; okay for analog/RF

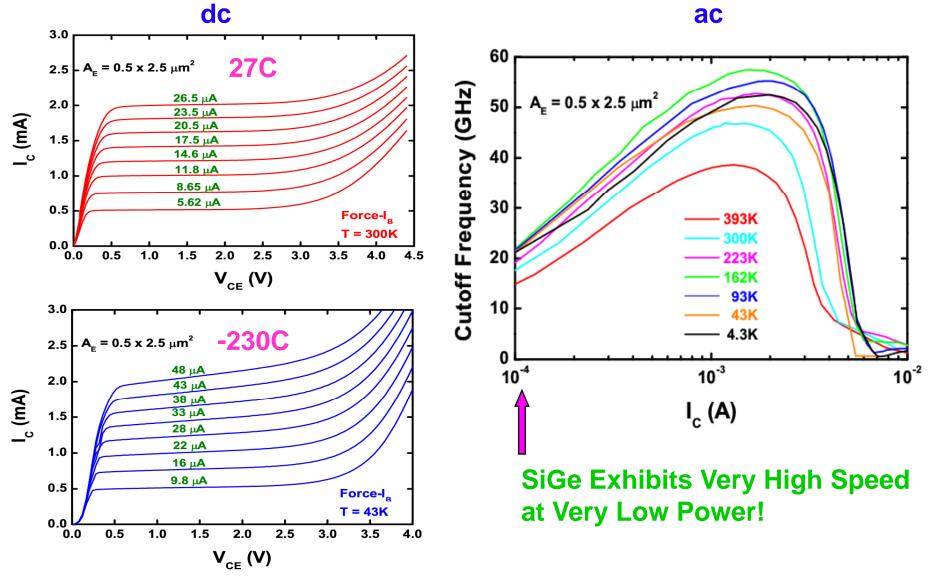

### Bulk SiGe BiCMOS

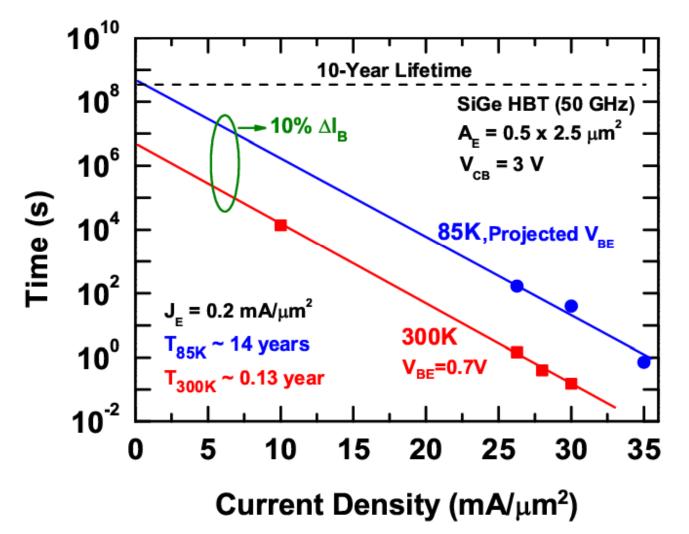

- SiGe HBT performance improves with cooling (across board)

- no issue with SiGe HBT cryo-T reliability

- CMOS here has the same pro's/con's as for bulk CMOS

- BiCMOS gives optimal division of labor for analog/RF/digital

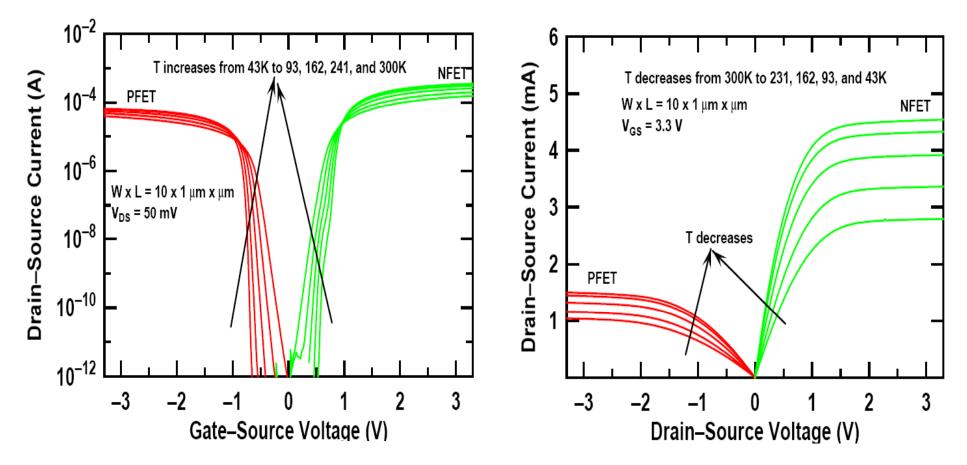

Cryo-CMOS Performance Georgia Institute of Technology

- CMOS Devices Function Well Down to 43 K

- Device Performance Improvement with Cooling (g<sub>m</sub>, μ, S)

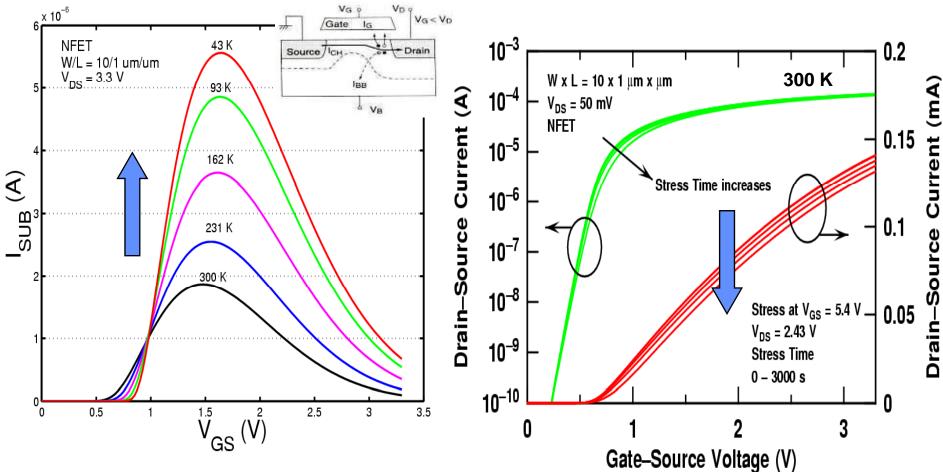

### **CMOS Reliability**

- I<sub>SUB</sub> is a Good Monitoring Parameter for HCE

- After Stress,  $I_d$  and  $g_m$  Decrease While  $V_T$  and S Increase

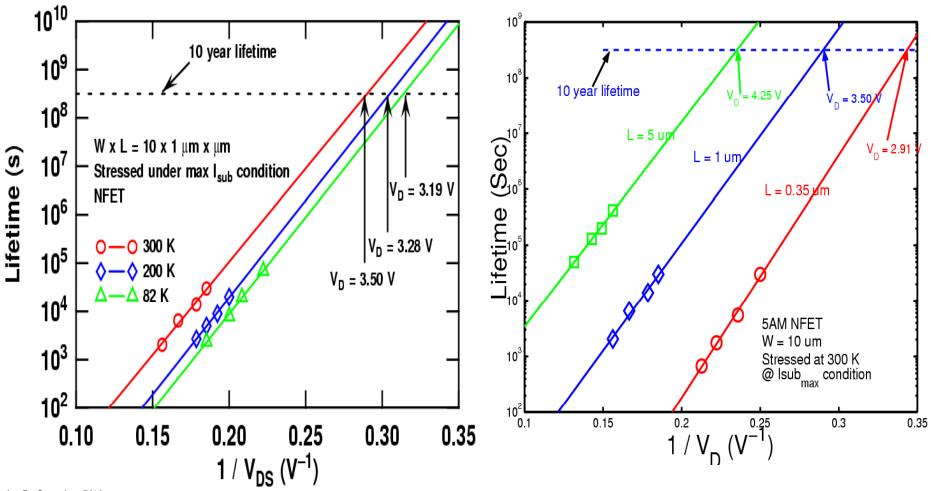

- Lifetime Decreases with Cooling at Fixed L

- Lifetime Decreases With L at Fixed T (Mitigation Path)

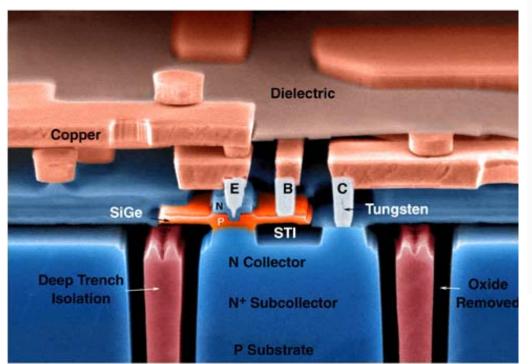

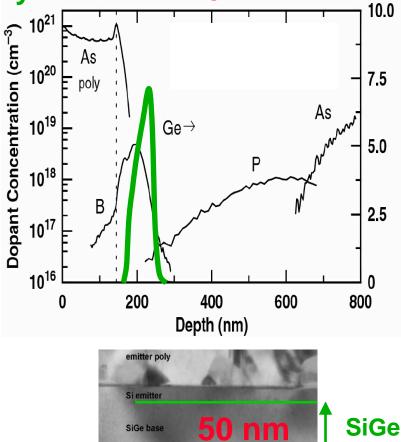

### **The SiGe HBT**

- Conventional Shallow and Deep Trench Isolation + CMOS BEOL

- Unconditionally Stable, SiGe Epitaxial Base Profile

- 100% Si Manufacturing Compatibility

- SiGe HBT + Si CMOS on wafer

#### SiGe = III-V Speed + Si Manufacturing Win-Win!

Ε

B

Si collector

John D. Cressler, 5/10

Germanium (%)

### **SiGe Performance Limits**

- Apparent Convergence of SiGe and III-V on Johnson Curve

- f<sub>T</sub> + f<sub>max</sub> > 1 THz in SiGe Is Clearly Possible (<u>at very modest lith</u>)

Realistic Goal = BV<sub>CEO</sub> > 1.5 V @ 500 GHz f<sub>T</sub> / f<sub>max</sub>

- 700 + f<sub>MAX</sub> = 1 THz - SiGe HB<sup>'</sup>Ts ETH SiGe HBTs InP HBTs (300 K 600 - 600 GHz = f<sub>MAX</sub> , UCSB Proto #3 500 S 4.5 K Σ Peak f<sup>MAX</sup> 300 K **BV**<sub>CEO</sub> UIUC Proto #2 1<sup>st</sup>-3<sup>rd</sup> gen: (300 K) 200 GHz Proto #1 200 4.5 K 750 GHz-V 100 150 GHz-V Р. 100 200 300 400 500 600 700 100 200 300 500 1000 Peak f<sub>+</sub> (GHz) f<sub>T</sub> (GHz)

Georgia Institute of Technology

### SiGe HBTs at Cryo-T

#### **First Generation SiGe HBT**

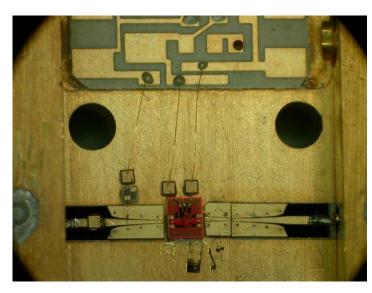

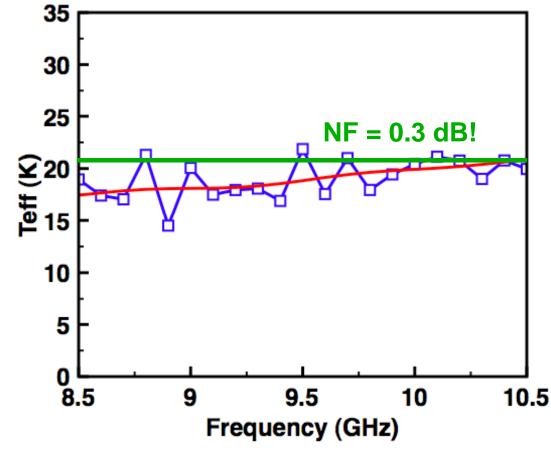

### X-band LNA Operation at 15 K (Not Yet Optimized!)

- **T<sub>eff</sub> < 20 K** (noise T)

- NF < 0.3 dB

- Gain > 20 dB

- *dc* power < 2 mW</li>

Collaboration with S. Weinreb, Cal Tech

This SiGe LNA is Also Rad-Hard!

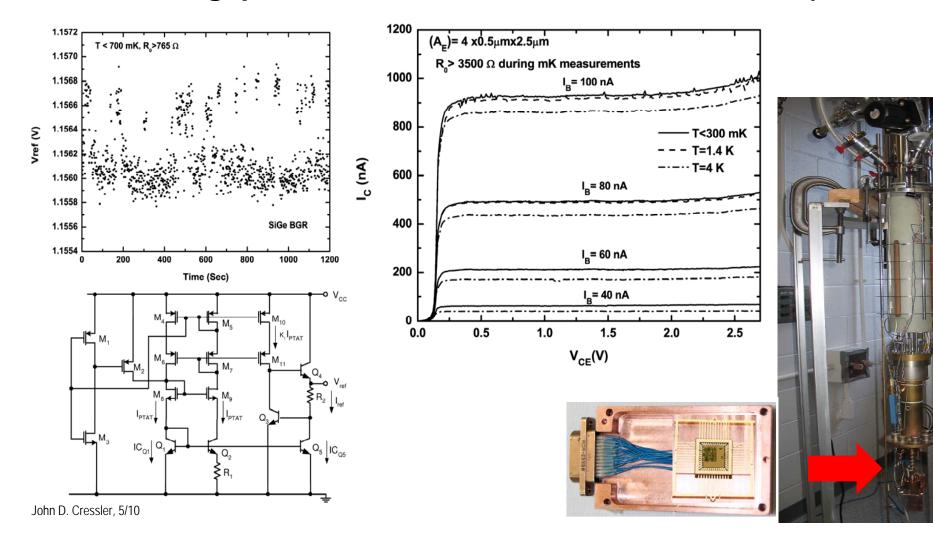

### **Operation at Sub-1K!**

- SiGe HBT Works Just Fine Down to 300 mK!

- SiGe Bandgap Reference Circuit Also Works! (700 mK)

• SiGe HBT Reliability Fine at Cryo-T

#### John D. Cressler, 5/10

#### Supports Many Sensor Types:

Temperature, Strain, Pressure, Acceleration, Vibration, Heat Flux, Position, etc.

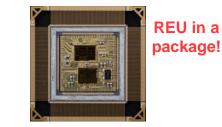

Use This SiGe REU as a Remote Vehicle Health Monitoring Node

### **Specifications**

- 5" x 3" x 6.75" = 101 in<sup>3</sup>

- 11 kg

- 17 Watts

- -55°C to +125°C

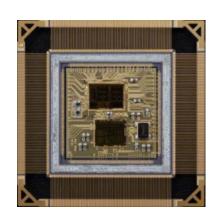

SiGe Analog

front end die

- Our SWAP Goals 1.5" x 1.5" x 0.5" = 1.1 in<sup>3</sup> (100x)

- < 1 kg (10x)

- < 2 Watts (10x)</li>

- -180°C to +125°C, rad tolerant

**SiGe Digital**

control die

The ETDP SiGe Remote

**Electronics Unit. 2010**

Georgia Institute of Technology

**The X-33**

Unit, BAE Systems,

**circa 1998**

X-33

**Remote Health**

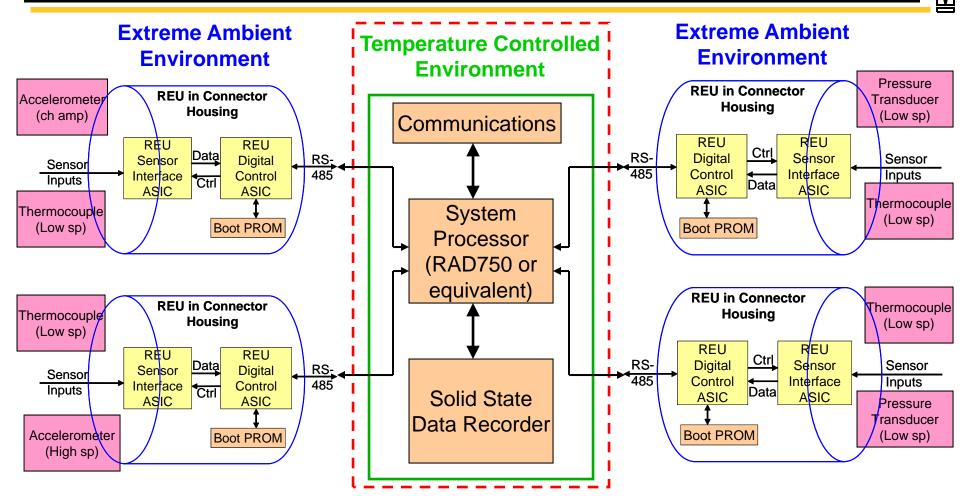

# **SiGe REU Architecture**

Georgia Institute of Technology

#### **Major Advantages:**

- Eliminates Warm Box (size, weight, and power; allows de-centralized architecture)

- Significant Wiring Reduction (weight, reliability, simplifies testing & diagnostics)

- Commonality (easily adapted from one system to the next)

- We now know how to build robust, reliable, complex mixed-signal (analog, digital, RF) electronics to operate at Titan temperatures

- We can provide <u>warm-box free</u> "electronic suites" for a wide class of instrument / sensor / control / comm needs that can provide <u>dramatic</u> reductions in SWAP

### **Complex On-Surface Electronics** analog, digital, RF, power, etc.

- < 1.0 in<sup>2</sup>

- < 100 g

- < 1-2 W for electronics SYSTEMS

**Read:** Environmental Invariance (e.g., 90 K)

- Old Idea: one big, heavy, power hungry science package with lots of instruments drops to the surface

- New Idea: identify a "few" (or lots!) target science sensor/instruments (e.g., lab on a chip) that can be packaged at <u>small</u> size and <u>low</u> power and then deploy a "platoon" of such small <u>environmentally invariant</u> science packages by parachute to the surface (land and lake boat with a sail?), each of which have <u>low-power</u> RF links (operating at ambient) for comm from package-to-package or package-to-balloon or package-to-orbiter

- Design small science packages to run off batteries for "long" duration operation, and perhaps even enabled to scavenge energy if desperate (beam RF from orbiter?)